# IGBT Chip in NPT-technology

#### **FEATURES:**

- 1200V NPT technology 175µm chip

- low turn-off losses

- short tail current

- positive temperature coefficient

- · easy paralleling

- integrated gate resistor

# This chip is used for:

• IGBT Modules

# Applications:

• drives, SMPS, resonant applications

| Chip Type      | V <sub>CE</sub> | I <sub>Cn</sub> | Die Size                    | ie Size Package |                       |

|----------------|-----------------|-----------------|-----------------------------|-----------------|-----------------------|

| SIGC81T120R2CS | 1200V           | 50A             | 9.08 X 8.98 mm <sup>2</sup> | sawn on foil    | Q67050-<br>A4050-A001 |

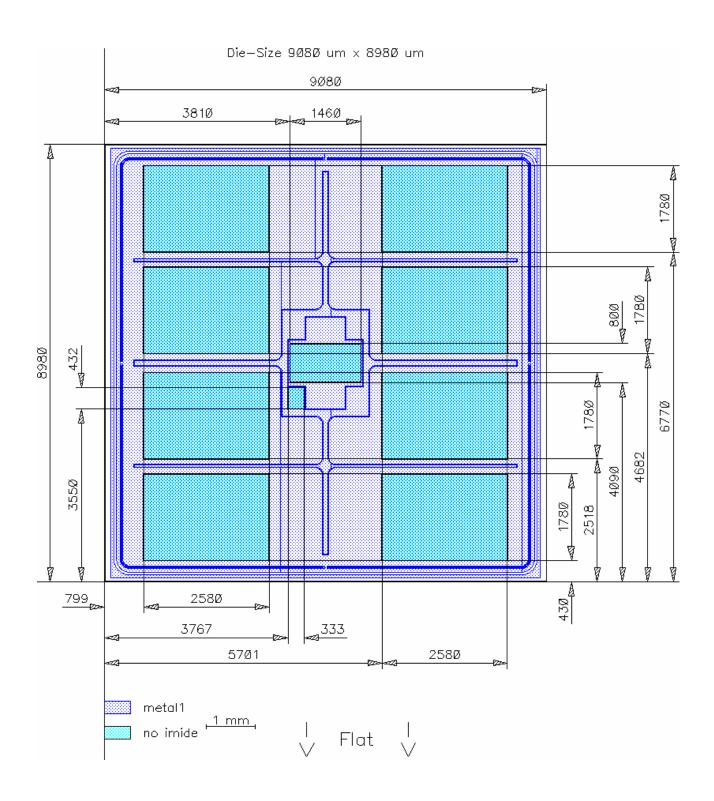

### **MECHANICAL PARAMETER:**

| Raster size                     | 9.08 X 8.98                                                                               | mm <sup>2</sup>                                                      |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| Emitter pad size                | 8 x (2.6 x 1.78)                                                                          |                                                                      |  |  |  |

| Gate pad size                   | 1.46 x 0.8                                                                                |                                                                      |  |  |  |

| Area total / active             | 81.5 / 63.5                                                                               |                                                                      |  |  |  |

| Thickness                       | 180                                                                                       | μm                                                                   |  |  |  |

| Wafer size                      | 150                                                                                       | mm                                                                   |  |  |  |

| Flat position                   | 90                                                                                        | grd                                                                  |  |  |  |

| Max.possible chips per wafer    | 167 pcs                                                                                   |                                                                      |  |  |  |

| Passivation frontside           | Photoimide                                                                                |                                                                      |  |  |  |

| Emitter metallization           | 3200 nm Al Si 1%                                                                          |                                                                      |  |  |  |

| Collector metallization         | 1400 nm Ni Ag –system suitable for epoxy and soft solder die b                            | 1400 nm Ni Ag –system suitable for epoxy and soft solder die bonding |  |  |  |

| Die bond                        | electrically conductive glue or solder                                                    |                                                                      |  |  |  |

| Wire bond                       | AI, <500μm                                                                                |                                                                      |  |  |  |

| Reject Ink Dot Size             | Ø 0.65mm; max 1.2mm                                                                       |                                                                      |  |  |  |

| Recommended Storage Environment | store in original container, in dry nitrogen, < 6 month at an ambient temperature of 23°C |                                                                      |  |  |  |

### **MAXIMUM RATINGS:**

| Parameter                                                             | Symbol             | Value            | Unit |

|-----------------------------------------------------------------------|--------------------|------------------|------|

| Collector-emitter voltage, T <sub>j</sub> =25 °C                      | V <sub>CE</sub>    | 1200             | V    |

| DC collector current, limited by T <sub>jmax</sub>                    | I <sub>C</sub>     | 1)               | Α    |

| Pulsed collector current, t <sub>p</sub> limited by T <sub>jmax</sub> | I <sub>cpuls</sub> | 150              | А    |

| Gate emitter voltage                                                  | V <sub>GE</sub>    | ±20              | V    |

| Operating junction and storage temperature                            | $T_j$ , $T_{stg}$  | -55 <b>+</b> 150 | °C   |

<sup>1)</sup> depending on thermal properties of assembly

# STATIC CHARACTERISTICS (tested on chip), $T_j$ =25 °C, unless otherwise specified:

| Parameter                            | Symbol               | Conditions                                             | Value |      |      | Unit |

|--------------------------------------|----------------------|--------------------------------------------------------|-------|------|------|------|

| i arameter                           | - Cymbol             | Conditions                                             | min.  | typ. | max. |      |

| Collector-emitter breakdown voltage  | V <sub>(BR)CES</sub> | V <sub>GE</sub> =0V , I <sub>C</sub> =3mA              | 1200  |      |      |      |

| Collector-emitter saturation voltage | V <sub>CE(sat)</sub> | V <sub>GE</sub> =15V, I <sub>C</sub> =50A              | 2.7   | 3.2  | 3.7  | V    |

| Gate-emitter threshold voltage       | $V_{\rm GE(th)}$     | I <sub>C</sub> =2mA , V <sub>GE</sub> =V <sub>CE</sub> | 4.5   | 5.5  | 6.5  |      |

| Zero gate voltage collector current  | I <sub>CES</sub>     | V <sub>CE</sub> =1200V , V <sub>GE</sub> =0V           |       |      | 6    | μA   |

| Gate-emitter leakage current         | I <sub>GES</sub>     | V <sub>CE</sub> =0V , V <sub>GE</sub> =20V             |       |      | 300  | nA   |

| Integrated gate resistor             | R <sub>Gint</sub>    |                                                        |       | 5    | 7    | Ω    |

## **ELECTRICAL CHARACTERISTICS** (tested at component):

| Parameter                    | Symbol | Conditions            | Value |      |      | Unit  |

|------------------------------|--------|-----------------------|-------|------|------|-------|

| raiametei                    | Symbol | Conditions            | min.  | typ. | max. | Oille |

| Input capacitance            | Ciss   | V <sub>CE</sub> =25V, | -     | 3.3  |      | nF    |

| Output capacitance           | Coss   | $V_{GE}=0V$ ,         | -     | 0.5  |      |       |

| Reverse transfer capacitance | Crss   | f=1MHz                | -     | 0.22 |      |       |

## SWITCHING CHARACTERISTICS (tested at component), Inductive Load

| Parameter           | Symbol       | Conditions 1)                                     | Value |      |      | Unit |

|---------------------|--------------|---------------------------------------------------|-------|------|------|------|

| raiametei           | Symbol       | Conditions                                        | min.  | typ. | max. |      |

| Turn-on delay time  | $t_{d(on)}$  | <i>T</i> <sub>j</sub> =125°C                      | -     | 60   |      | ns   |

| Rise time           | $t_{\rm r}$  | V <sub>CC</sub> =600V,                            | -     | 50   |      |      |

| Turn-off delay time | $t_{d(off)}$ | I <sub>C</sub> =50A,<br>V <sub>GE</sub> =-15/15V, | -     | 400  |      |      |

| Fall time           | $t_{f}$      | $R_{\rm G}$ = 15 $\Omega$                         | -     | 60   |      |      |

<sup>&</sup>lt;sup>1)</sup> values also influenced by parasitic L- and C- in measurement and package.

#### **CHIP DRAWING:**

### **FURTHER ELECTRICAL CHARACTERISTICS:**

| This chip data sheet refers to the device data sheet              | Eupec | FP50R12KS4C |  |  |  |  |  |

|-------------------------------------------------------------------|-------|-------------|--|--|--|--|--|

| DESCRIPTION:                                                      |       |             |  |  |  |  |  |

| AQL 0,65 for visual inspection according to failure catalog       |       |             |  |  |  |  |  |

| Electrostatic Discharge Sensitive Device according to MIL-STD 883 |       |             |  |  |  |  |  |

| Test-Normen Villach/Prüffeld                                      |       |             |  |  |  |  |  |

Published by Infineon Technologies AG, Bereich Kommunikation St.-Martin-Strasse 53, D-81541 München © Infineon Technologies AG 2002 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives world-wide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and / or maintain and sustain and / or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.